Thursday, March 30th SBC Theatre

14:10 - 14:50 Power Amplifier Efficiency Enhancement Techniques Based on Load Modulation

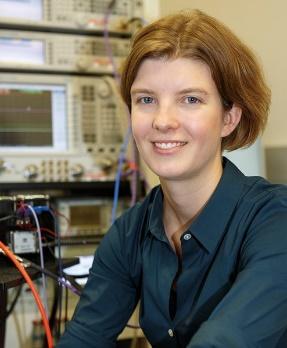

Dr. Taylor Barton, University of Colorado Boulder

This tutorial will discuss efficiency enhancement techniques for RF power amplifiers (PAs), focusing on those using modulation of the load impedance to maintain high efficiency into power back-off. The discussion will begin with an overview of conventional techniques such as direct load modulation, Doherty, and outphasing PAs, and describe PA design techniques when the load impedance is not constant. The tutorial will also highlight recently developed PA architectures for load modulation.

Taylor Barton is an Assistant Professor at the University of Colorado Boulder, with expertise in RF/microwave active circuit design. She received the Sc. B., M.Eng., E.E., and Sc.D degrees from the Massachusetts Institute of Technology, Cambridge, MA. Prior to joining CU Boulder, she was a Postdoctoral Associate in the MIT Microsystems Technology Laboratories and was an Assistant Professor at the University of Texas at Dallas from 2014 to 2016. She is the technical program chair of the Texas Symposium, and a member of MTT Technical Committee 5: Microwave high-power techniques, IEEE Young Professionals, and IEEE Women in Engineering.